# SONY

#### AC-DC Controller

# **CXA3809M**

#### **Description**

The CXA3809M has optimum configuration to realize various power supply circuits easily and compactly by including Power-factor correction, resonant controller and various protection function in one package. (Applications: Power supply circuit, etc.)

#### **Features**

- ◆ Power-factor correction

- · Multiplierless critical conduction mode (CRM) control

- Supports W/W input

- Restart timer

- Maximum frequency limit (during overcurrent detection)

- Continuous overcurrent detection protection function

- ◆ Resonant controller

- Timer-latch over current protection

- Soft start function

- · Adjustment minimum frequency limit

- · Pulse over current load detection

- · Out of resonance prevention function at start-up

- ◆ Common

- Adjacent 2-pin short protection

- Various protection functions including overvoltage and overcurrent

- AC off detection

- PFC-OK signal output

#### Structure

BiCMOS silicon monolithic IC

#### **Package**

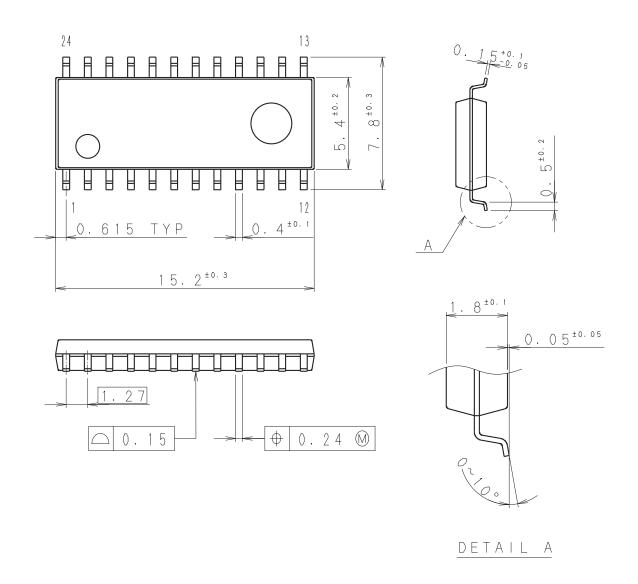

24-pin SOP

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 - E09504

# **Absolute Maximum Ratings**

| Item                                          | Symbol | Rating            | Unit | Remarks                                                                                                         |

|-----------------------------------------------|--------|-------------------|------|-----------------------------------------------------------------------------------------------------------------|

| Maximum supply voltage                        | VCC    | 24.0              | V    | VCC                                                                                                             |

| VCC pin voltage                               | VCCIN  | -0.3 to VCC + 0.3 | V    | AC_DETIN, AC_DETOUT,<br>AC_VRMS, PFC_OK, MODE                                                                   |

| Driver output pin voltage                     | VOUT   | -0.3 to VCC + 0.3 | ٧    | PFC_OUT, RM_OUTP,<br>RM_OUTN                                                                                    |

| Power supply pin voltage for internal circuit | VREF   | -0.3 to +7.0      | ٧    | VREF                                                                                                            |

| VREF pin voltage                              | VREFIN | -0.3 to +7.0      | V    | PFC_OVP, PFC_CS, PFC_VAO,<br>PFC_TONMAX, PFC_VSENSE,<br>RM_OFFADJ, RM_RT, RM_SS,<br>RM_CS, RM_CSGND,<br>RM_FMIN |

| ZCD current                                   | Izco   | ±7                | mA   | PFC_ZCD                                                                                                         |

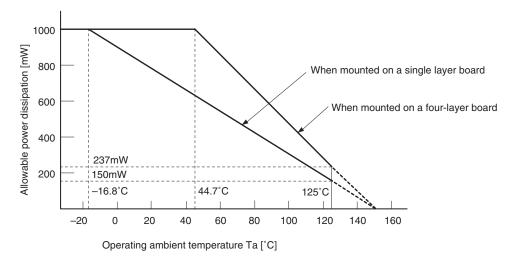

| Allowable power dissipation                   | Po     | *1                | mW   | (See the thermal derating curve.)                                                                               |

| Operating ambient temperature range           | Topt   | -30 to +125       | °C   |                                                                                                                 |

| Junction temperature                          | Tjmax  | +150              | °C   |                                                                                                                 |

| Storage temperature                           | Tstg   | -55 to +150       | °C   |                                                                                                                 |

<sup>\*1</sup> Allowable power dissipation reduction characteristics

Glass fabric base epoxy board,  $76\text{mm} \times 114\text{mm}$ , t = 1.6mm

# **Recommended Operating Conditions**

| Item                                | Symbol | Rating       | Unit | Remarks |

|-------------------------------------|--------|--------------|------|---------|

| Supply voltage (VCC system)         | VCC    | 12.0 to 18.0 | V    |         |

| Operating ambient temperature range | Topt   | -25 to +85   | °C   |         |

| Junction temperature                | Tj     | -25 to +125  | °C   |         |

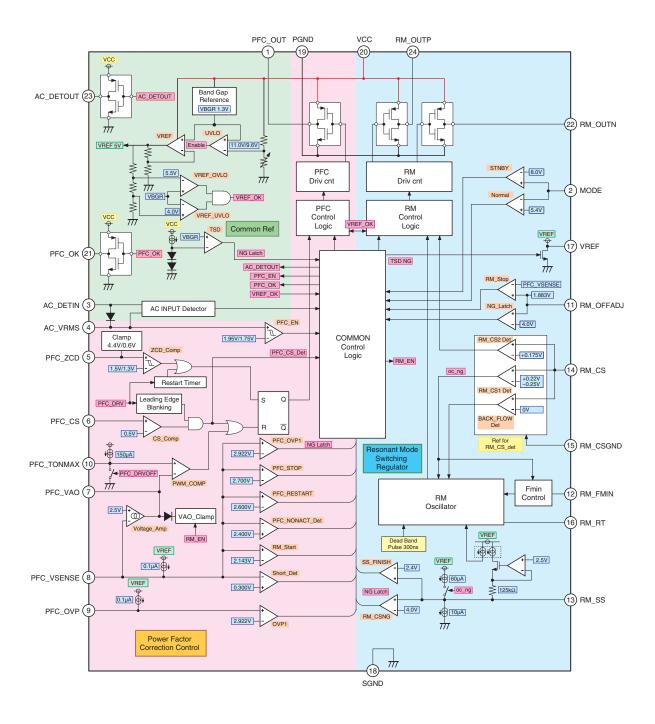

## **Block Diagram**

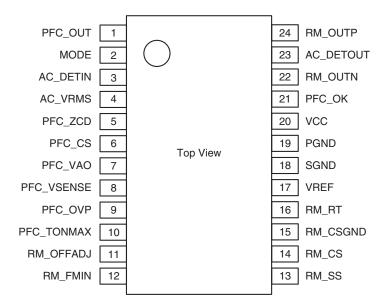

# **Pin Configuration**

CXA3809M

# Pin Table

| Pin<br>No. | Pin name   | Description                                                          | Connection end of protective element |

|------------|------------|----------------------------------------------------------------------|--------------------------------------|

| 1          | PFC_OUT    | PFC MOSFET gate driver output                                        | _                                    |

| 2          | MODE       | Mode determination                                                   | VCC, SGND                            |

| 3          | AC_DETIN   | AC voltage sense input                                               | VCC, SGND                            |

| 4          | AC_VRMS    | AC peak voltage sense and PFC enable                                 | VCC, SGND                            |

| 5          | PFC_ZCD    | PFC zero current detect input                                        | VCC, SGND                            |

| 6          | PFC_CS     | PFC current sense input                                              | VREF, SGND                           |

| 7          | PFC_VAO    | PFC voltage control error amplifier output                           | VREF, SGND                           |

| 8          | PFC_VSENSE | PFC output voltage sense input                                       | VREF, SGND                           |

| 9          | PFC_OVP    | PFC output overvoltage sense input                                   | VREF, SGND                           |

| 10         | PFC_TONMAX | PFC maximum ON time control                                          | VREF, SGND                           |

| 11         | RM_OFFADJ  | Resonant controller stop voltage adjustment and abnormal latch input | VREF, SGND                           |

| 12         | RM_FMIN    | Resonant controller minimum frequency setting                        | VREF, SGND                           |

| 13         | RM_SS      | Resonant controller soft start and overcurrent timer-latch setting   | VREF, SGND                           |

| 14         | RM_CS      | Resonant controller current sense input                              | VREF                                 |

| 15         | RM_CSGND   | Resonant controller current sense ground                             | VREF                                 |

| 16         | RM_RT      | Resonant controller frequency control                                | VREF, SGND                           |

| 17         | VREF       | Internal supply voltage                                              | VCC, SGND                            |

| 18         | SGND       | Signal ground                                                        | (PGND)                               |

| 19         | PGND       | PFC, RM driver ground                                                | (SGND)                               |

| 20         | VCC        | Power supply input                                                   | SGND                                 |

| 21         | PFC_OK     | PFC-OK signal output                                                 | _                                    |

| 22         | RM_OUTN    | Resonant controller Low-side MOSFET driver output                    | _                                    |

| 23         | AC_DETOUT  | AC off detect signal output                                          | _                                    |

| 24         | RM_OUTP    | Resonant controller High-side MOSFET driver output                   | _                                    |

# **Pin Description**

| Pin<br>No. | Symbol   | I/O | Standard pin voltage   | Equivalent circuit                | Description                                                                              |

|------------|----------|-----|------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| 1          | PFC_OUT  | 0   | VCC to GND             | VCC VREF Peh PFC_OUT Noh Noh PGND | PFC MOSFET gate driver output (Connect to the NMOS gate for PFC)                         |

| 2          | MODE     | I   | VCC to GND             | WCC  MODE  Noch  SGND             | Mode select input (GND connection:     Normal sequence VCC connection:     Standby mode) |

| 3          | AC_DETIN | ı   | VCC to GND             | VCC VREF AC_DETIN SGND            | AC voltage input<br>(Connect to AC input detection<br>resistor)                          |

| 4          | AC_VRMS  | I/O | (VCC – 2.0V)<br>to GND | AC_VRMS AC_VRMS SGND              | AC peak voltage sense and PFC enable (Connect to peak voltage hold capacitor)            |

| Pin<br>No. | Symbol     | I/O | Standard pin voltage                         | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                |

|------------|------------|-----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 5          | PFC_ZCD    | ı   | 4.4V to 0.6V                                 | VCC VREF  PFC_ZCD  SGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PFC zero current detect input (Connect to boost inductor of auxiliary winding)                             |

| 6          | PFC_CS     | I   | VREF to GND                                  | PFC_CS  BYREF  PFC_CS  SGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PFC current sense input (Connect to the detection side of current sense resistor)                          |

| 7          | PFC_VAO    | 0   | 3.2V to GND                                  | PFC_VAO  The part of the part | PFC voltage control error amplifier output (Connect a phase compensation circuit: between PFC_VAO and GND) |

| 8          | PFC_VSENSE | I   | VREF to GND<br>During steady-<br>state: 2.5V | PFC_VSENSE Pch SGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PFC output voltage sense input (Connect to PFC output detection resistor)                                  |

| 9          | PFC_OVP    | I   | VREF to GND<br>During steady-<br>state: 2.5V | PFC_OVP Pch SGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PFC output overvoltage sense input (Connect to PFC output detection resistor)                              |

| Pin<br>No. | Symbol     | I/O | Standard pin voltage                                   | Equivalent circuit         | Description                                                                                                              |

|------------|------------|-----|--------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 10         | PFC_TONMAX | I/O | 3.2V to GND                                            | PFC_TONMAX  Pch  Nch  SGND | PFC maximum ON time control (Connect to ON time control capacitor)                                                       |

| 11         | RM_OFFADJ  | I/O | VREF to GND                                            | RM_OFFADJ SGND             | Resonant controller stop voltage adjustment and abnormal latch input                                                     |

| 12         | RM_FMIN    | ı   | 1.2V                                                   | RM_FMIN SGND               | Resonant controller minimum frequency setting (Connect to minimum frequency control resistor)                            |

| 13         | RM_SS      | I/O | VREF to GND<br>During steady-<br>state: 2.5V           | RM_SS Pch Nch Pch SGND     | Resonant controller soft start<br>and overcurrent timer-latch<br>setting<br>(Connect to the capacitor for<br>soft start) |

| 14         | RM_CS      |     | V/PEE to 0.21/                                         | VREF Pch                   | Resonant controller current sense input (Connect to the resistor for current detection)                                  |

| 15         | RM_CSGND   | 1   | RM_CS<br>RM_CSGND Resonant consense ground (Connect to |                            | Resonant controller current sense ground (Connect to the resistor for current detection)                                 |

| Pin<br>No. | Symbol    | I/O | Standard pin voltage | Equivalent circuit          | Description                                                                                    |  |

|------------|-----------|-----|----------------------|-----------------------------|------------------------------------------------------------------------------------------------|--|

| 16         | RM_RT     | -   | (3.5V)               | VREF Peh Peh SGND           | Resonant controller frequency control (Connect to the photo coupler for output feedback)       |  |

| 17         | VREF      | 0   | 5.0V                 | VCC  VREF  VREF  17  SGND   | Internal supply voltage output (Connect to the capacitor for stabilization)                    |  |

| 18         | SGND      |     | _                    | _                           | Signal ground                                                                                  |  |

| 19         | PGND      |     |                      | 1                           | Driver ground                                                                                  |  |

| 20         | VCC       | 1   | ĺ                    | 1                           | Power supply input                                                                             |  |

| 21         | PFC_OK    | 0   | VCC to GND           | VCC  VREF Pch Pch AC_DETOUT | PFC-OK signal output                                                                           |  |

| 23         | AC_DETOUT | )   | VOC 10 GIVE          | SGND PGND                   | AC off detect signal output                                                                    |  |

| 22         | RM_OUTN   | 0   | VCC to GND           | VCC  RM_OUTN RM_OUTP        | Resonant controller Low-side<br>MOSFET driver output<br>(Connect to the drive<br>transformer)  |  |

| 24         | RM_OUTP   | )   | VOC IO GIND          | Nch PGND                    | Resonant controller High-side<br>MOSFET driver output<br>(Connect to the drive<br>transformer) |  |

### **Electrical Characteristics**

#### **♦** Shared Blocks

(Unless otherwise specified, the conditions are  $Ta = 27^{\circ}C$ , VCC = 12V, MODE = GND)

# 1. Current Consumption (VCC and PVCC pins)

| Item                                | Symbol | Measurement conditions                            | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------|---------------------------------------------------|------|------|------|------|

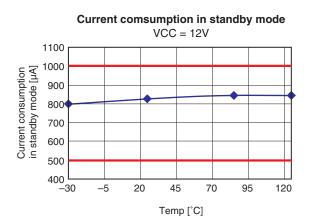

| Current consumption in standby mode | Istb   | MODE = VCC                                        |      | 700  | 1000 | μА   |

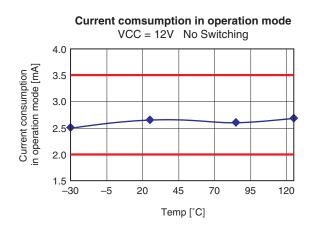

| Operating current consumption       | lact   | AC_DETIN = 1.0V, PFC_VSENSE = 1.0V * No Switching |      | 3.0  | 3.5  | mA   |

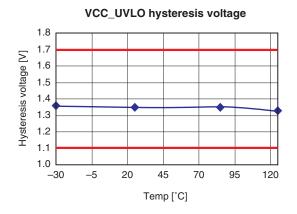

# 2. Under Voltage Lock Out Circuit Block (VCC pin)

| Item             | Symbol    | Measurement conditions | Min. | Тур. | Max. | Unit |

|------------------|-----------|------------------------|------|------|------|------|

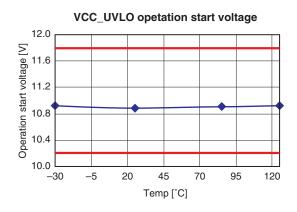

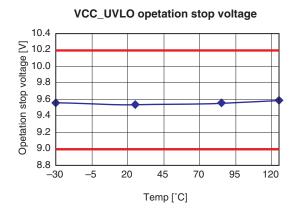

| Turn-on voltage  | Vact      |                        | 10.2 | 11.0 | 11.8 | V    |

| Turn-off voltage | Voff      |                        | 9.0  | 9.6  | 10.2 | V    |

| Hysteresis       | Vact-Voff | Vact – Voff            | 1.1  | 1.4  | 1.7  | V    |

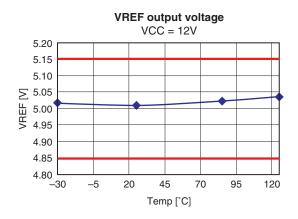

# 3. Reference Voltage Output Circuit Block (VREF pin)

| Item                                 | Symbol  | Measurement conditions            | Min. | Тур. | Max. | Unit |

|--------------------------------------|---------|-----------------------------------|------|------|------|------|

| Output voltage                       | Vvref   |                                   | 4.85 | 5.00 | 5.15 | V    |

| Input stability                      | Vline   | VCC = 10.5V to 18V                | _    | 10   | 30   | mV   |

| Load stability                       | Vload   | Iload = 0.1m to 5mA               |      | 20   | 50   | mV   |

| Pin voltage when NG latch (When TSD) | Vvrefng | lout = 10mA<br>(Design guarantee) | _    | 0.1  | 0.5  | V    |

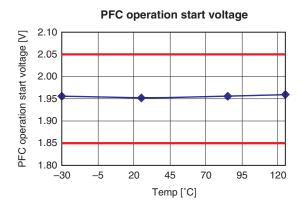

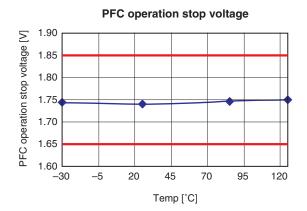

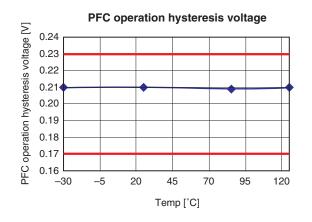

# 4. AC Input Detection Circuit Block (AC\_DETIN pin)

| Item                                  | Symbol  | Measurement conditions                                 | Min.  | Тур.  | Max.  | Unit |

|---------------------------------------|---------|--------------------------------------------------------|-------|-------|-------|------|

| PFC operation start                   | Vpfcon  | AC_DETIN peak voltage (rise)                           | 1.85  | 1.95  | 2.05  | V    |

| and stop voltage                      | Vpfcoff | AC_DETIN peak voltage (fall)                           | 1.65  | 1.75  | 1.85  | V    |

| Hysteresis                            | Vpfchys | Vpfcok – Vpfcoff                                       | 0.17  | 0.20  | 0.23  | V    |

| AC detection reference voltage High 1 | Vthach1 | AC_VRMS = 7.5V                                         | 4.675 | 4.875 | 5.075 | V    |

| AC detection reference voltage Low 1  | Vthacl1 | AC_VRMS = 7.5V                                         | 3.175 | 3.375 | 3.575 | V    |

| AC detection reference voltage High 2 | Vthach2 | AC_VRMS = 2.0V                                         | 1.1   | 1.3   | 1.5   | V    |

| AC detection reference voltage Low 2  | Vthacl2 | AC_VRMS = 2.0V                                         | 0.7   | 0.9   | 1.1   | V    |

| AC off detection delay time 1         | Tdlyac1 | AC_DETIN < AC_VRMS × 45% (State A)                     | 4     | 5     | 6     | ms   |

| AC off detection delay time 2         | Tdlyac2 | AC_VRMS × 65% > AC_DETIN<br>> AC_VRMS × 45% (State B1) | 4     | 5     | 6     | ms   |

| AC off detection delay time 3         | Tdlyac3 | AC_VRMS × 65% > AC_DETIN<br>> AC_VRMS × 45% (State B2) | 6.4   | 8     | 9.6   | ms   |

| AC off detection delay time 4         | Tdlyac4 | AC_DETIN > AC_VRMS × 65% (State C)                     | 20    | 25    | 30    | ms   |

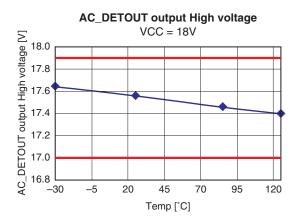

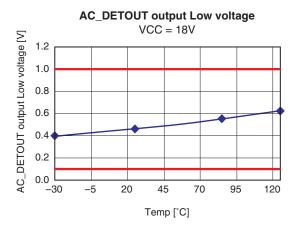

# 5. AC Off Detect Signal Output Circuit Block (AC\_DETOUT pin)

| Item                | Symbol  | Measurement conditions  | Min. | Тур. | Max. | Unit |

|---------------------|---------|-------------------------|------|------|------|------|

| Output Low voltage  | Vacoutl | VCC = 18V, lout = 10mA  | _    | 0.5  | 1.0  | V    |

| Output High voltage | Vacouth | VCC = 18V, lout = -10mA | 17.0 | 17.5 | _    | V    |

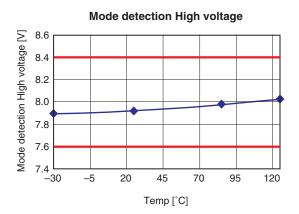

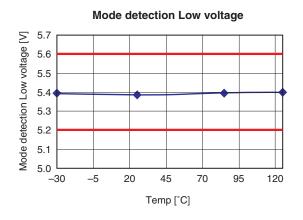

# 6. MODE Pin Voltage Detection Circuit Block (MODE pin)

| Item                        | Symbol | Measurement conditions | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------------------------|------|------|------|------|

| MODE detection voltage Low  | Vmodel |                        | 5.2  | _    | 5.6  | V    |

| MODE detection voltage High | Vmodeh |                        | 7.6  |      | 8.4  | V    |

| Internal pull-up resistor   | Rmode  | MODE = 0.1V            | 35   | 50   | 65   | kΩ   |

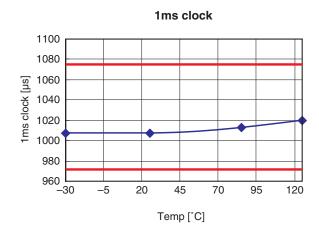

### 7. Clock Timer

| Item      | Symbol | Measurement conditions | Min. | Тур. | Max. | Unit |

|-----------|--------|------------------------|------|------|------|------|

| 1ms clock | Tclock |                        | 972  | 1024 | 1075 | μs   |

#### **♦ PFC Block**

(Unless otherwise specified, the conditions are  $Ta = 27^{\circ}C$ , VCC = 12V, MODE = GND)

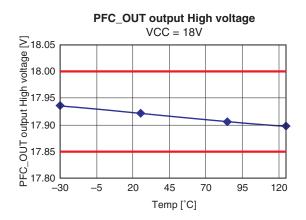

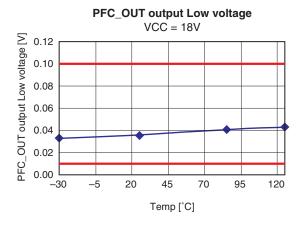

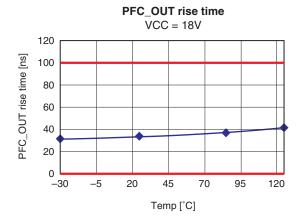

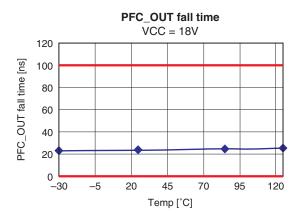

# 8. PFC Output Circuit Block (PFC\_OUT pin)

| Item                | Symbol | Measurement conditions    | Min.  | Тур. | Max. | Unit |

|---------------------|--------|---------------------------|-------|------|------|------|

| Output Low voltage  | Vpoutl | VCC = 18V, lout = 10mA    | _     | 0.03 | 0.1  | V    |

| Output High voltage | Vpouth | VCC = 18V, lout = -10mA   | 17.85 | 17.9 |      | V    |

| Rise time *1        | Tpoutr | VCC = 18V, CLOAD = 1000pF |       | 35   | 100  | ns   |

| Fall time *1        | Tpoutf | VCC = 18V, CLOAD = 1000pF | _     | 25   | 100  | ns   |

$<sup>^{*1}</sup>$   $\,$  Rise time and fall time use VCC  $\times$  0.1 to VCC  $\times$  0.9 as the judgment voltages.

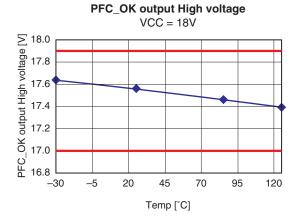

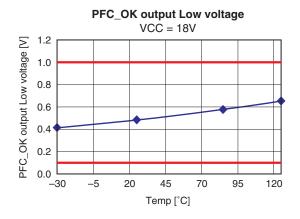

## 9. PFC-OK Signal Circuit Block (PFC\_OK pin)

| Item                | Symbol  | Measurement conditions  | Min. | Тур. | Max. | Unit |

|---------------------|---------|-------------------------|------|------|------|------|

| Output Low voltage  | Vacoutl | VCC = 18V, lout = 10mA  | _    | 0.5  | 1.0  | V    |

| Output High voltage | Vacouth | VCC = 18V, lout = -10mA | 17.0 | 17.5 |      | V    |

### 10. AC Peak Voltage Sense Circuit Block (AC\_VRMS pin)

| Item                              | Symbol | Measurement conditions | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|------------------------|------|------|------|------|

| Internal pull-down resistor value | Rvrms  | AC_VRMS = 1.0V         | 0.6  | 0.8  | 1.0  | МΩ   |

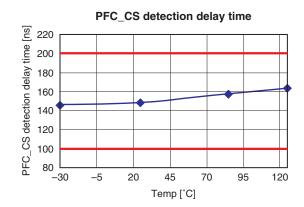

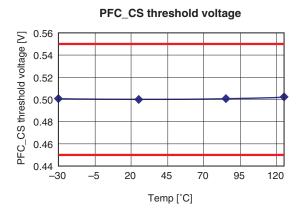

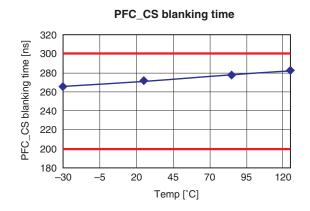

### 11. PFC Overcurrent Detection Circuit Block (PFC\_CS pin)

| Item                    | Symbol | Measurement conditions                                        | Min. | Тур. | Max. | Unit |

|-------------------------|--------|---------------------------------------------------------------|------|------|------|------|

| Input threshold voltage | Vthcs  |                                                               | 0.45 | 0.50 | 0.55 | V    |

| Blanking time           | Tleb   | PFC_CS = 1.0V                                                 | 200  | 250  | 300  | ns   |

| Delay time              | Tcsdly | CS to DRV<br>PFC_CS = 0V ⇒ 1V<br>(Rectangular waveform input) | 100  | 150  | 200  | ns   |

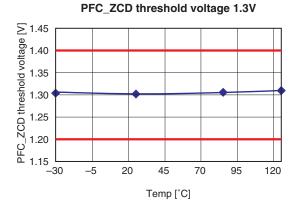

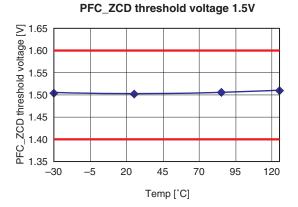

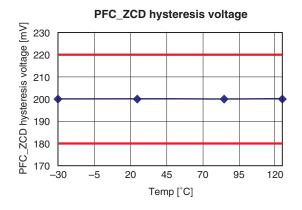

# 12. PFC Zero Current Detection Circuit Block (PFC\_ZCD pin)

| Item                                                         | Symbol  | Measurement conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|---------|------------------------|------|------|------|------|

| Input threshold voltage                                      | Vthzcd  |                        | 1.2  | 1.3  | 1.4  | V    |

| Hysteresis                                                   | Vzcdhys |                        | 180  | 200  | 220  | mV   |

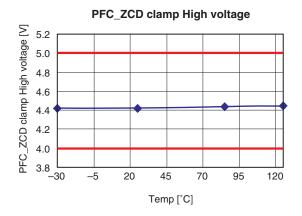

| Clamp High voltage                                           | Vclph   | I = 3mA                | 4.0  | 4.4  | 5.0  | V    |

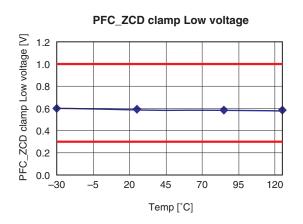

| Clamp Low voltage                                            | Vclpl   | I = -3mA               | 0.3  | 0.6  | 1.0  | V    |

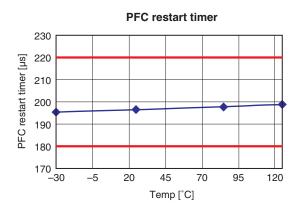

| Restart timer delay                                          | Tstart  |                        | 180  | 200  | 220  | μS   |

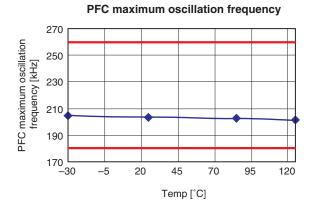

| Maximum oscillation frequency (During overcurrent detection) | Fpfcmax | PFC_CS = 1.0V          | 180  | 220  | 260  | kHz  |

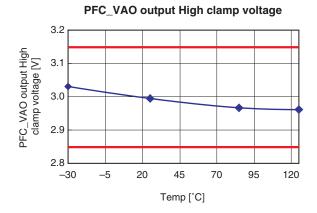

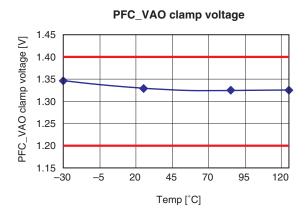

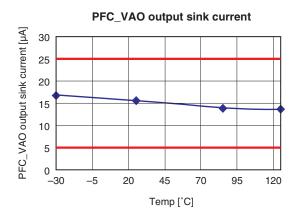

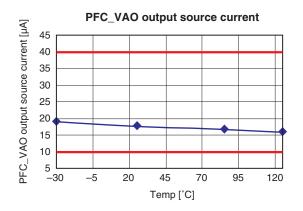

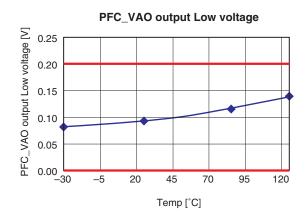

# 13. Error Amplifier Output Circuit Block for PFC Voltage Control (PFC\_VAO pin)

| Item                      | Symbol | Measurement conditions                                       | Min. | Тур. | Max. | Unit          |

|---------------------------|--------|--------------------------------------------------------------|------|------|------|---------------|

| Trans-conductance         | Vvaogm | (Design guarantee)                                           | _    | (90) | _    | μ <b>A</b> /V |

| Output High clamp voltage | Vvaoh  | PFC_VSENSE = 2.45V                                           | 2.85 | 3.0  | 3.15 | V             |

| Clamp voltage at start-up | Vvao1  | PFC_VSENSE = 2.0V<br>(When other than resonant<br>operation) | 1.2  | 1.3  | 1.4  | V             |

| Source current            | Ivaosc | PFC_VSENSE = 2.2V,<br>PFC_VAO = 0.5V                         | 10   | 20   | 40   | μА            |

| Output Low voltage        | Vvaol  | PFC_VSENSE = 2.55V                                           | 0    | _    | 0.2  | V             |

| Sink current              | Ivaosk | PFC_VSENSE = 2.65V,<br>PFC_VAO = 3.0V                        | 5    | 15   | 25   | μА            |

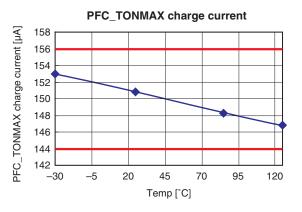

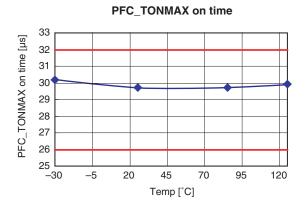

### 14. PFC Maximum ON Time Control Circuit Block (PFC\_TONMAX pin)

| Item               | Symbol     | Measurement conditions                    | Min. | Тур. | Max. | Unit |

|--------------------|------------|-------------------------------------------|------|------|------|------|

| Charge current     | Itoncharge | PFC_TONMAX = 0.1V                         | 144  | 150  | 156  | μΑ   |

| Discharge time     | Tdischarge | Ct = 1500pF,<br>PFC_TONMAX = 3.2V to 0.1V | _    | _    | 150  | ns   |

| PFC output ON time | Ton        | PFC_VSENSE = 2.45V,<br>Ct = 1500pF        | 26   | 29   | 32   | μS   |

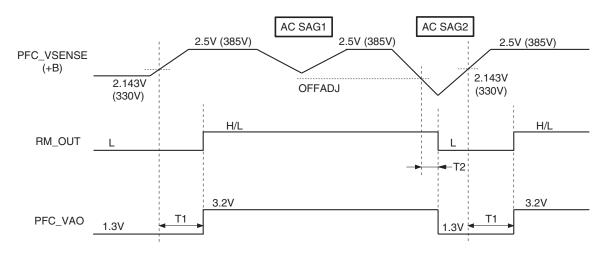

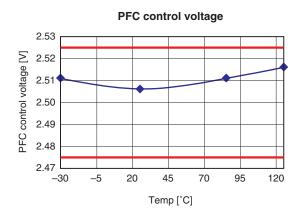

# 15. PFC Output Voltage Detection Circuit Block (PFC\_VSENSE pin)

| Item                                        | Symbol     | Measurement conditions | Min.  | Тур.  | Max.  | Unit |

|---------------------------------------------|------------|------------------------|-------|-------|-------|------|

| PFC overvoltage detection voltage           | Vovp1      |                        | 2.849 | 2.922 | 2.995 | V    |

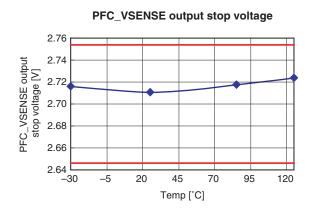

| PFC stop voltage                            | Vovp2      |                        | 2.646 | 2.7   | 2.754 | V    |

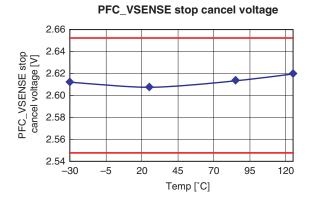

| PFC stop cancel voltage                     | Vovp2hys   |                        | 2.548 | 2.6   | 2.652 | V    |

| PFC control voltage                         | Vpfccnt    |                        | 2.475 | 2.5   | 2.525 | V    |

| PFC non-operating detection voltage         | Vpfcnonact |                        | 2.280 | 2.4   | 2.520 | V    |

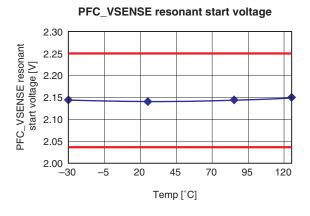

| Resonant controller operation start voltage | Vrmstart   |                        | 2.036 | 2.143 | 2.250 | ٧    |

| Resonant controller operation stop voltage  | Vrmstop    | When RM_OFFADJ = open  | 1.789 | 1.883 | 1.977 | ٧    |

| Pin short-circuit detection                 | Vshort     |                        | 0.2   | 0.3   | 0.4   | V    |

| Pull-up current                             | Ivs        | PFC_VSENSE = 0.1V      | 0.05  | 0.1   | 0.2   | μА   |

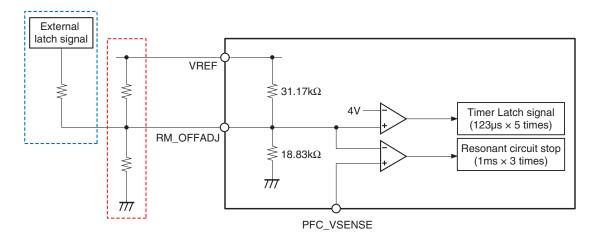

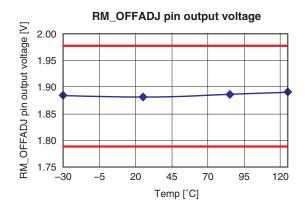

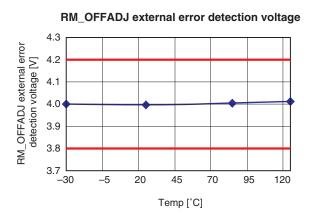

# 16. Resonant Controller Stop Voltage Adjustment Circuit Block (RM\_OFFADJ pin)

| Item                                       | Symbol    | Measurement conditions | Min.  | Тур.  | Max.  | Unit |

|--------------------------------------------|-----------|------------------------|-------|-------|-------|------|

| Output voltage                             | Vrmoff    |                        | 1.789 | 1.883 | 1.977 | V    |

| Latch voltage for external error detection | Voffadjng |                        | 3.8   | 4.0   | 4.2   | V    |

# 17. PFC Overvoltage Detection Circuit Block (PFC\_OVP pin)

| Item                              | Symbol | Measurement conditions | Min.  | Тур.  | Max.  | Unit |

|-----------------------------------|--------|------------------------|-------|-------|-------|------|

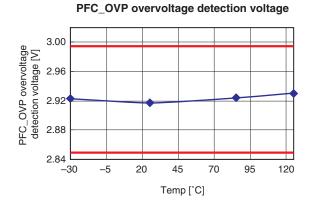

| PFC overvoltage detection voltage | Vovp11 |                        | 2.849 | 2.922 | 2.995 | V    |

| Pull-up current                   | lovp   | PFC_VSENSE = 0.1V      | 0.05  | 0.1   | 0.2   | μΑ   |

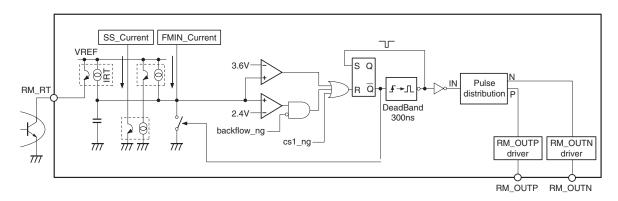

#### ♦ Resonant Controller Block

(Unless otherwise specified, the conditions are Ta =  $27^{\circ}$ C, VCC = 12V, MODE = GND, RM\_RT = OPEN, Rfmin = 20k $\Omega$ )

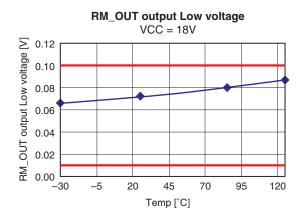

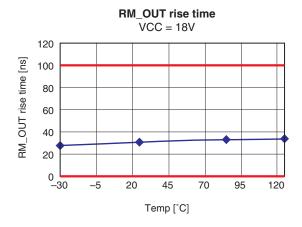

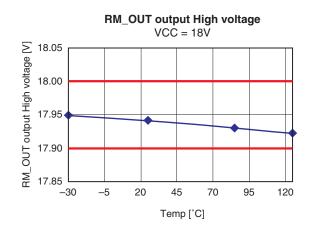

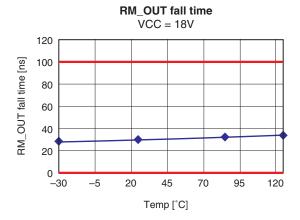

## 18. Resonant Controller Output Circuit Block (RM\_OUTP, RM\_OUTN pins)

| Item                | Symbol | Measurement conditions    | Min. | Тур.  | Max. | Unit |

|---------------------|--------|---------------------------|------|-------|------|------|

| Output Low voltage  | Vroutl | VCC = 18V, lout = 10mA    | _    | 0.05  | 0.1  | V    |

| Output High voltage | Vrouth | VCC = 18V, lout = -10mA   | 17.9 | 17.95 | _    | V    |

| Rise time           | Vroutr | VCC = 18V, CLOAD = 1000pF |      | 35    | 100  | ns   |

| Fall time           | Vroutf | VCC = 18V, CLOAD = 1000pF | _    | 35    | 100  | ns   |

Note) Rise time is judged at VCC  $\times$  0.1 and fall time is judged at VCC  $\times$  0.9 respectively.

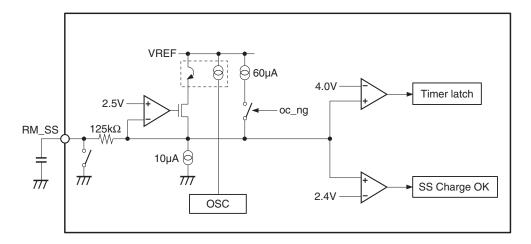

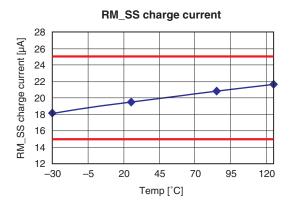

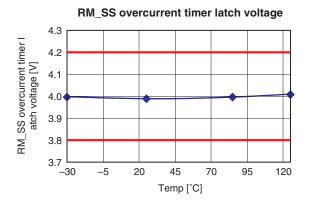

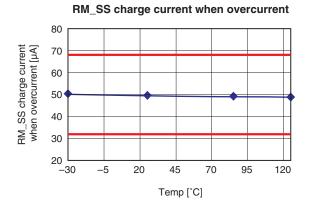

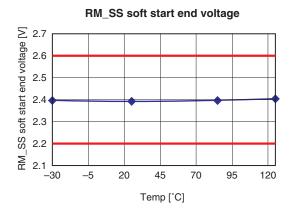

#### 19. Resonant Controller Soft Start Circuit Block (RM\_SS pin)

| Item                                          | Symbol      | Measurement conditions  | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|-------------|-------------------------|------|------|------|------|

| Soft start current                            | Irmss       | RM_SS = 0V              | 15   | 20   | 25   | μΑ   |

| Clamp voltage                                 | Vrmss       |                         | 2.3  | 2.5  | 2.7  | V    |

| Soft start end detection voltage              | Vssok       |                         | 2.2  | 2.4  | 2.6  | V    |

| Overcurrent timer latch detection voltage     | Vtimerlatch |                         | 3.8  | 4.0  | 4.2  | V    |

| Charging current during overcurrent detection | locc        | RM_CS = 0.3V, SS = 3.0V | 32   | 50   | 68   | μА   |

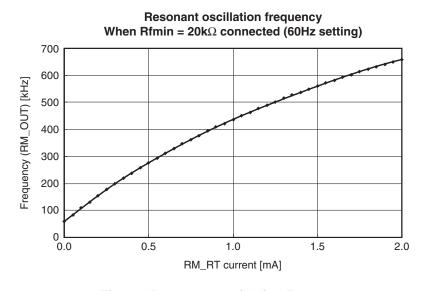

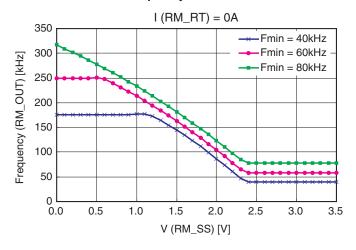

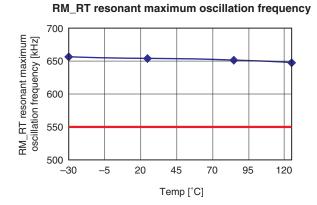

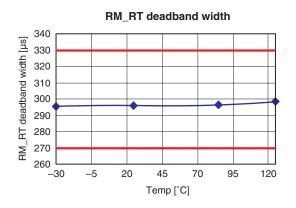

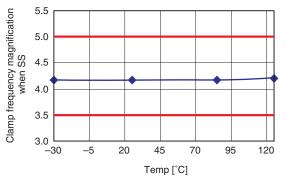

### 20. Resonant Controller Frequency Control Circuit Block (RM\_RT pin)

| Item                                               | Symbol | Measurement conditions                         | Min. | Тур. | Max. | Unit  |

|----------------------------------------------------|--------|------------------------------------------------|------|------|------|-------|

| Maximum oscillation frequency                      | Frmmax | Irt = 2mA, Rfmin = $15k\Omega$                 | 550  | _    | _    | kHz   |

| Deadband width                                     | Tdb    |                                                | 270  | 300  | 330  | ns    |

| Multiple number of clamp frequency when soft start | Fclamp | f0/f4<br>(f0: RM_SS = 0V,<br>f4: RM_SS = 2.5V) | 3.5  | 4.5  | 5    | times |

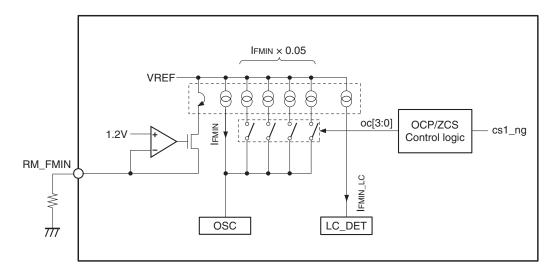

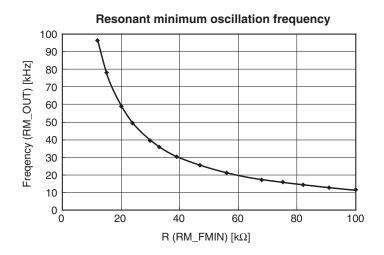

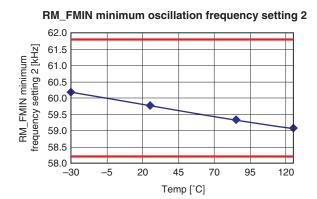

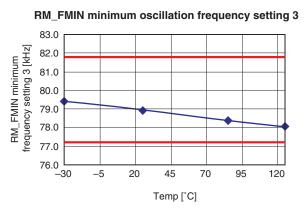

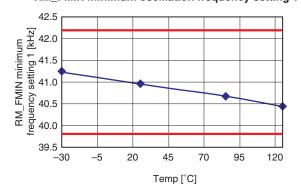

#### 21. Resonant Controller Minimum Frequency Adjustment Circuit Block (RM\_FMIN pin)

| Item                | Symbol | Measurement conditions | Min.  | Тур. | Max.  | Unit |

|---------------------|--------|------------------------|-------|------|-------|------|

| Setting frequency 1 | Fmin1  | Rfmin = $30k\Omega$    | (-3%) | 41   | (+3%) | kHz  |

| Setting frequency 2 | Fmin2  | Rfmin = $20k\Omega$    | (-3%) | 60   | (+3%) | kHz  |

| Setting frequency 3 | Fmin3  | Rfmin = $15k\Omega$    | (-3%) | 79.5 | (+3%) | kHz  |

| Output voltage      | Vfmin  |                        | 1.0   | 1.2  | 1.4   | V    |

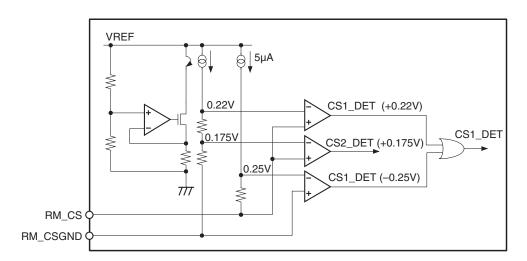

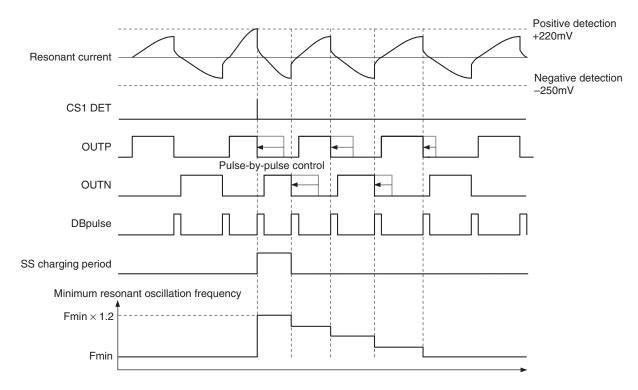

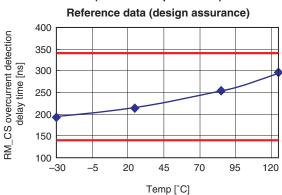

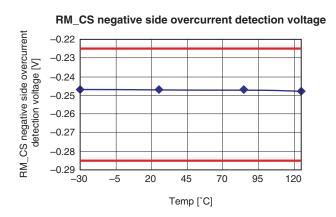

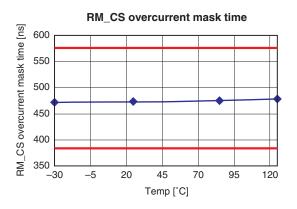

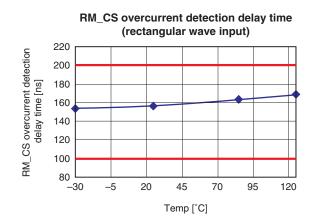

### 22. Resonant Controller Current Detection Circuit Block (RM\_CS pin, RM\_CSGND pin)

| Item                                          | Symbol   | Measurement conditions                                   | Min.   | Тур.   | Max.   | Unit |

|-----------------------------------------------|----------|----------------------------------------------------------|--------|--------|--------|------|

| Positive side detection                       | Vcs1p    | When RM_OUTP = High                                      | 0.209  | 0.220  | 0.231  | V    |

| Negative side detection                       | Vcs1n    | When RM_OUTN = High                                      | -0.285 | -0.250 | -0.225 | V    |

| Detection delay time                          | Tcsdly   | CS to DRV<br>RM_CS = −0.3V ↔ 0.3V<br>(Rectangular input) | 100    | 150    | 200    | ns   |

| Detection mask time                           | Tcsmask  | RM_CS = 0.3V                                             | 384    | 480    | 576    | ns   |

| Continuous load detection voltage             | Vcs2     | When RM_OUTP = High                                      | 0.158  | 0.175  | 0.193  | V    |

| Continuous load detection time                | Tcs2     | (When the time corresponds to 2.1s × 5 times)            |        | (10)   |        | s    |

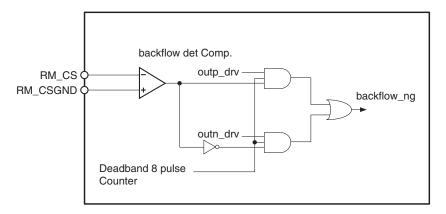

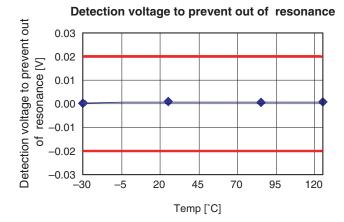

| Out of resonance prevention detection voltage | Vcsbfdet | When resonance start-up                                  | -0.02  | 0      | 0.02   | V    |

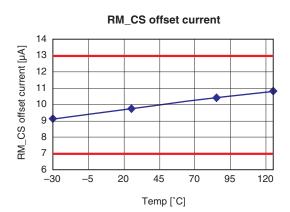

| RS_CS pin offset current                      | Icspos   | RM_CS = 0.1V                                             | 7      | 10     | 13     | μА   |

| RS_CSGND pin offset current                   | Icsneg   | RM_CSGND = 0.1V                                          | 7      | 10     | 13     | μА   |

Note) ◆ The shipping inspection is performed at room temperature. (The design is guaranteed with respect to temperature fluctuation.)

<sup>◆</sup> The notation "±" of application current shown in the measurement conditions indicates that "-" is outflow current from the IC and "+" is inflow current to it.

### 23. List of Electrical Characteristics

| ltem                                         |            | ification ra<br>Ta = 27°C |       |       | ratings<br>°C) (*1) | Unit      |    |

|----------------------------------------------|------------|---------------------------|-------|-------|---------------------|-----------|----|

|                                              | Min.       | Тур.                      | Max.  | Min.  | Тур.                | Max.      |    |

| Current consumption (VCC, PVCC pins)         |            |                           |       |       |                     | •         |    |

| Current consumption in standby mode          | _          | 700                       | 1000  | _     | 700                 | 1000      | μА |

| Current consumption in operation mode        | _          | 3                         | 3.5   | _     | 3                   | 3.5       | mA |

| Low voltage misoperation prevention circu    | it block ( | VCC pin)                  |       |       | •                   | •         | •  |

| Operation start voltage                      | 10.2       | 11                        | 11.8  | 10.2  | 11                  | 11.8      | V  |

| Operation stop voltage                       | 9          | 9.6                       | 10.2  | 9     | 9.6                 | 10.2      | V  |

| Hysteresis width                             | 1.1        | 1.4                       | 1.7   | 1.1   | 1.4                 | 1.7       | V  |

| Reference voltage output block (VREF pin)    |            |                           |       |       |                     | •         | I. |

| Output voltage                               | 4.85       | 5                         | 5.15  | 4.85  | 5                   | 5.15      | V  |

| Input stability                              | _          | 10                        | 30    | 0     | 10                  | 30.5 (*2) | mV |

| Load stability                               | _          | 20                        | 50    | _     | 20                  | 50        | mV |

| Pin voltage when NG latch (When TSD)         | _          | 0.1                       | 0.5   | _     | 0.1                 | 0.5       | V  |

| AC input detection circuit block (AC_DETIN   | N pin)     |                           |       | ı     | ı                   |           |    |

| DEC eneration start voltage                  | 1.85       | 1.95                      | 2.05  | 1.85  | 1.95                | 2.05      | V  |

| PFC operation start voltage                  | 1.65       | 1.75                      | 1.85  | 1.65  | 1.75                | 1.85      | V  |

| Hysteresis width                             | 0.17       | 0.2                       | 0.23  | 0.17  | 0.2                 | 0.23      | V  |

| AC detection reference voltage High 1        | 4.675      | 4.875                     | 5.075 | 4.675 | 4.875               | 5.075     | V  |

| AC detection reference voltage Low 1         | 3.175      | 3.375                     | 3.575 | 3.175 | 3.375               | 3.575     | V  |

| AC detection reference voltage High 2        | 1.1        | 1.3                       | 1.5   | 1.1   | 1.3                 | 1.5       | V  |

| AC detection reference voltage Low 2         | 0.7        | 0.9                       | 1.1   | 0.7   | 0.9                 | 1.1       | V  |

| AC off detection delay time 1                | 4          | 5                         | 6     | 4     | 5                   | 6         | ms |

| AC off detection delay time 2                | 4          | 5                         | 6     | 4     | 5                   | 6         | ms |

| AC off detection delay time 3                | 6.4        | 8                         | 9.6   | 6.4   | 8                   | 9.6       | ms |

| AC off detection delay time 4                | 20         | 25                        | 30    | 20    | 25                  | 30        | ms |

| AC input error detection output circuit bloc | k (AC_D    | ETOUT pi                  | in)   |       | •                   | •         |    |

| Output Low voltage                           | _          | 0.5                       | 1     | _     | 0.5                 | 1         | V  |

| Output High voltage                          | 17         | 17.5                      | _     | 17    | 17.5                | _         | V  |

| Mode pin determination circuit block (MOD    | E pin)     |                           |       |       |                     |           |    |

| MODE detection voltage Low                   | 5.2        | _                         | 5.6   | 5.2   | _                   | 5.6       | V  |

| MODE detection voltage High                  | 7.6        | _                         | 8.4   | 7.6   | _                   | 8.4       | V  |

| Internal pull-up resistor value              | 35         | 50                        | 65    | 35    | 50                  | 65        | kΩ |

| Clock timer                                  |            |                           |       |       |                     |           |    |

| 1ms clock                                    | 972        | 1024                      | 1075  | 972   | 1024                | 1075      | μS |

| PFC output circuit block (PFC_OUT pin)       |            |                           |       |       |                     |           |    |

| Output Low voltage                           | _          | 0.03                      | 0.1   |       | 0.03                | 0.1       | V  |

| Output High voltage                          | 17.85      | 17.9                      | _     | 17.85 | 17.9                | _         | V  |

| Rise time                                    |            | 35                        | 100   | _     | 35                  | 100       | ns |

|                                              | <u> </u>   |                           |       |       |                     | <u> </u>  |    |

| ltem                                                         |          | ification ra |          | Design guarant<br>(Ta = -25 to + |          |               | Unit          |

|--------------------------------------------------------------|----------|--------------|----------|----------------------------------|----------|---------------|---------------|

|                                                              | Min.     | Тур.         | Max.     | Min.                             | Тур.     | Max.          |               |

| PFC-OK signal circuit block (PFC_OK pin)                     | •        | •            | •        |                                  |          |               |               |

| Output Low voltage                                           | _        | 0.5          | 1        | _                                | 0.5      | 1             | V             |

| Output High voltage                                          | 17       | 17.5         | _        | 17                               | 17.5     | _             | V             |

| AC peak voltage monitor circuit block (AC_                   | VRMS pi  | n)           | <u> </u> |                                  |          | !             |               |

| Internal pull-up resistor value                              | 0.6      | 0.8          | 1        | 0.6                              | 0.8      | 1             | ΜΩ            |

| PFC overcurrent detection circuit block (PI                  | FC_CS pi | n)           | <u>I</u> |                                  | Į.       | ı             |               |

| Input threshold voltage                                      | 0.45     | 0.5          | 0.55     | 0.45                             | 0.5      | 0.55          | V             |

| Blanking time                                                | 200      | 250          | 300      | 200                              | 250      | 300           | ns            |

| Delay time                                                   | 100      | 150          | 200      | 100                              | 150      | 200           | ns            |

| PFC zero current detection circuit block (P                  | FC_ZCD   | pin)         | <u> </u> |                                  | <u>!</u> | !             |               |

| Input threshold voltage                                      | 1.2      | 1.3          | 1.4      | 1.2                              | 1.3      | 1.4           | V             |

| Hysteresis width                                             | 180      | 200          | 220      | 180                              | 200      | 220           | mV            |

| Clamp High voltage                                           | 4        | 4.4          | 5        | 4                                | 4.4      | 5             | V             |

| Clamp Low voltage                                            | 0.3      | 0.6          | 1        | 0.3                              | 0.6      | 1             | V             |

| Restart timer delay                                          | 180      | 200          | 220      | 180                              | 200      | 220           | μS            |

| Maximum oscillation frequency (When overcurrent is detected) | 180      | 220          | 260      | 180                              | 220      | 260           | kHz           |

| Error amplifier output circuit block for PFC                 | voltage  | control (F   | PFC_VAO  | pin)                             | I        |               |               |

| Trans-conductance                                            | _        | (90)         | _        |                                  | (90)     |               | μ <b>A</b> /V |

| Output High voltage                                          | 2.85     | 3            | 3.15     | 2.85                             | 3        | 3.15          | V             |

| Clamp voltage at startup                                     | 1.2      | 1.3          | 1.4      | 1.2                              | 1.3      | 1.4           | V             |

| Output source current                                        | 10       | 20           | 40       | 10                               | 20       | 40            | μА            |

| Output Low voltage                                           | 0        | _            | 0.2      | 0                                | _        | 0.2           | V             |

| Output sink current                                          | 5        | 15           | 25       | 5                                | 15       | 25            | μА            |

| PFC maximum ON time control circuit bloc                     | k (PFC_T | ONMAX        | pin)     |                                  |          | ļ.            |               |

| Pin charging current                                         | 144      | 150          | 156      | 144                              | 150      | 158 (*2)      | μΑ            |

| Pin discharging current                                      | _        | _            | 150      | _                                | _        | 150           | ns            |

| On time                                                      | 26       | 29           | 32       | 26                               | 29       | 32            | μS            |

| PFC output voltage detection circuit block                   | (PFC_VS  | ENSE pir     | 1)       |                                  | Į.       | ı             |               |

| PFC overvoltage detection                                    | 2.849    | 2.922        | 2.995    | 2.849                            | 2.922    | 2.995         | V             |

| PFC stop voltage                                             | 2.646    | 2.7          | 2.754    | 2.646                            | 2.7      | 2.754         | V             |

| PFC stop cancel voltage                                      | 2.548    | 2.6          | 2.652    | 2.548                            | 2.6      | 2.652         | V             |

| PFC control voltage                                          | 2.475    | 2.5          | 2.525    | 2.475                            | 2.5      | 2.526<br>(*2) | V             |

| PFC non-operating detection voltage                          | 2.28     | 2.4          | 2.52     | 2.28                             | 2.4      | 2.52          | V             |

| Resonant controller operation start voltage                  | 2.036    | 2.143        | 2.25     | 2.036                            | 2.143    | 2.25          | V             |

| Resonant controller operation stop voltage                   | 1.789    | 1.883        | 1.977    | 1.789                            | 1.883    | 1.977         | V             |

| Pin short-circuit detection                                  | 0.2      | 0.3          | 0.4      | 0.2                              | 0.3      | 0.4           | V             |

| Pin pull-up current                                          | 0.05     | 0.1          | 0.2      | 0.05                             | 0.1      | 0.2           | μА            |

| ltem                                            |             | ification ra |           | Design guarantee rating (Ta = -25 to +85°C) (*1) |       |               | Unit  |

|-------------------------------------------------|-------------|--------------|-----------|--------------------------------------------------|-------|---------------|-------|

|                                                 | Min.        | Тур.         | Max.      | Min.                                             | Тур.  | Max.          |       |

| Resonant controller stop voltage adjustme       | nt circuit  | block (R     | M_OFFAI   | OJ pin)                                          |       |               |       |

| RM_OFFADJ pin output voltage                    | 1.789       | 1.883        | 1.977     | 1.789                                            | 1.883 | 1.977         | V     |

| Latch voltage for external error detection      | 3.8         | 4            | 4.2       | 3.8                                              | 4     | 4.2           | V     |

| PFC overvoltage detection circuit block (PI     | FC_OVP      | oin)         | •         |                                                  | •     | •             |       |

| PFC overvoltage detection voltage               | 2.849       | 2.922        | 2.995     | 2.849                                            | 2.922 | 2.995         | V     |

| Pin pull-up current                             | 0.05        | 0.1          | 0.2       | 0.05                                             | 0.1   | 0.2           | μΑ    |

| Resonant controller output circuit block (R     | M_OUTP      | , RM_OU      | TN pins)  |                                                  | •     | •             | •     |

| Output Low voltage                              | _           | 0.05         | 0.1       | _                                                | 0.05  | 0.1           | V     |

| Output High voltage                             | 17.9        | 17.95        | _         | 17.9                                             | 17.95 | _             | V     |

| Rise time                                       | _           | 35           | 100       | _                                                | 35    | 100           | ns    |

| Fall time                                       | _           | 35           | 100       | _                                                | 35    | 100           | ns    |

| Resonant controller soft start circuit block    | (RM_SS      | pin)         |           | -                                                | •     | •             |       |

| Soft start current                              | 15          | 20           | 25        | 15                                               | 20    | 25            | μА    |

| Clamp voltage                                   | 2.3         | 2.5          | 2.7       | 2.3                                              | 2.5   | 2.7           | V     |

| Soft start end detection voltage                | 2.2         | 2.4          | 2.6       | 2.2                                              | 2.4   | 2.6           | V     |

| Overcurrent timer latch detection voltage       | 3.8         | 4            | 4.2       | 3.8                                              | 4     | 4.2           | V     |

| Charge current when overcurrent is detected     | 32          | 50           | 68        | 32                                               | 50    | 68            | μА    |

| Resonant controller soft start circuit block    | (RM_RT      | pin)         |           |                                                  |       |               |       |

| Maximum oscillation frequency                   | 550         | _            | _         | 550                                              | _     | _             | kHz   |

| Deadband width                                  | 270         | 300          | 330       | 270                                              | 300   | 330           | ns    |

| Clamp frequency magnification during soft start | 3.5         | 4.5          | 5         | 3.5                                              | 4.5   | 5             | times |

| Resonant controller minimum frequency ad        | djustmen    | t circuit b  | lock (RM  | _FMIN pir                                        | 1)    |               |       |

| Setting frequency 1                             | 39.77       | 41           | 42.23     | 39.46<br>(*2)                                    | 41    | 42.68<br>(*2) | kHz   |

| Setting frequency 2                             | 58.2        | 60           | 61.8      | 58.20                                            | 60    | 61.80         | kHz   |

| Setting frequency 3                             | 77.12       | 79.5         | 81.88     | 76.13<br>(*2)                                    | 79.5  | 81.88         | kHz   |

| Pin output voltage                              | 1           | 1.2          | 1.4       | 1                                                | 1.2   | 1.4           | V     |

| Resonant controller current detection circu     | ıit block ( | RM_CS p      | oin, RM_C | SGND pir                                         | າ)    |               |       |

| Positive side detection                         | 0.209       | 0.22         | 0.231     | 0.209                                            | 0.22  | 0.231         | V     |

| Negative side detection                         | -0.285      | -0.25        | -0.225    | -0.285                                           | -0.25 | -0.225        | V     |

| Detection delay time                            | 100         | 150          | 200       | 100                                              | 150   | 200           | ns    |

| Detection mask time                             | 384         | 480          | 576       | 384                                              | 480   | 576           | ns    |

| Continuous load detection voltage               | 0.158       | 0.175        | 0.193     | 0.158                                            | 0.175 | 0.193         | V     |

| Continuous load detection time                  | _           | (10)         | _         |                                                  | (10)  |               | s     |

| Out of resonance prevention detection voltage   | -0.02       | 0            | 0.02      | -0.02                                            | 0     | 0.02          | V     |

| RM_CS pin offset current                        | 7           | 10           | 13        | 7                                                | 10    | 13            | μΑ    |

| RM_CSGND pin offset current                     | 7           | 10           | 13        | 7                                                | 10    | 13            | μА    |

$<sup>^{*1}</sup>$  Ratings are design guarantee values within this temperature range.

<sup>\*2</sup> Specification values at room temperature may not be satisfied because of temperature dependence.

## **Detailed Description of Each Block**

#### **♦ Common Circuit Block**

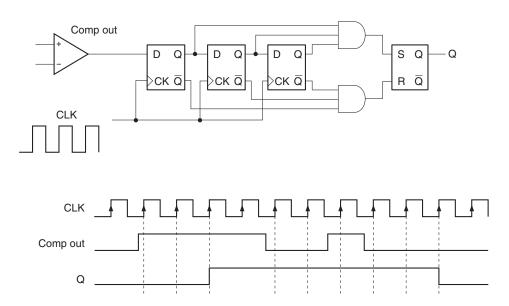

#### 1. Misdetection Prevention Circuit

Fig. 1. Equivalent Circuit Corresponded to 1ms  $\times$  3 Times

Fig. 1 above shows the equivalent circuit corresponded to  $1ms \times 3$  times.

When CLK has a 1ms cycle, comp out is monitored at the rising edge of every 1ms, and the output Q is defined when it reaches three times. The 5 times-corresponded circuit also operates using a similar system, so the approach is the same.

The clocks used for each setup time are generated by frequency dividing the 1MHz clock. The setup variance time of the 1ms  $\times$  3 times correspondence circuit in the example above is as follows. Variance of 2ms < setup time < 3ms occurs due to the comp out inversion timing. In addition, taking into account the basic clock 1kHz variance, the 1ms (1024 $\mu$ s) clock has variance of 0.972ms to 1.075ms ( $\pm$ 5%), so at the maximum variance the setup variance time is 1.944ms < setup time < 3.225ms.

Setup time of misdetection prevention counter (when the basic clock of 1MHz has no variance) used for this IC is shown below.

| <ul> <li>Corresponds to 1μs × 4 times 3μs to 4μs</li> </ul>                       |

|-----------------------------------------------------------------------------------|

| <ul> <li>Corresponds to 1μs × 16 times 15μs to 16μs</li> </ul>                    |

| <ul> <li>Corresponds to 128μs × 3 times 256μs to 384μs</li> </ul>                 |

| <ul> <li>Corresponds to 128μs × 5 times 512μs to 640μs</li> </ul>                 |

| ◆ Corresponds to 1ms × 3 times                                                    |

| ◆ Corresponds to 1ms × 5 times 4ms to 5ms                                         |

| • Corresponds to 4.1ms × 3 times 8.2ms to 12.3ms (Converted by 4.1ms for 4.096ms) |

| • Corresponds to 16ms × 4 times 48ms to 64ms (Converted by 16ms for 16.4ms)       |

| • Corresponds to 66ms × 8 times 462ms to 528ms (Converted by 66ms for 65.5ms)     |

| • Corresponds to 2.1s × 3 times 4.2s to 6.3s (Converted by 2.1s for 2.097s)       |

| <ul> <li>Corresponds to 2.1s × 5 times</li></ul>                                  |

#### 2. AC Detection Circuit Block

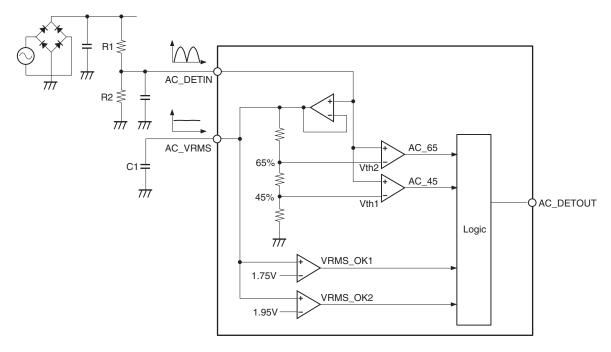

Fig. 2-1 shows the AC detection block equivalent circuit.

Fig. 2-1. AC Detection Block Equivalent Circuit

The AC detection circuit block detects the AC input voltage by directly monitoring the full-wave rectified AC input waveform.

The wave input to the AC\_DETIN pin is peak-held at the AC\_VRMS pin by a buffer circuit, and reference voltages equivalent to 45% (Vth1) and 65% (Vth2) of the peak value are generated internally. The AC input is constantly monitored to determine the voltage range by comparing these reference voltages and the AC\_DETIN pin voltage.

The AC\_VRMS pin voltage is compared with the internal reference voltages, and AC input is detected when the AC\_VRMS pin voltage is 1.95V or more, or AC OFF when 1.75V or less. When R1 =  $1000k\Omega$  and R2 =  $18k\Omega$  in Fig. 2-1, AC input is detected when VAC = 78Vrms or more.

In addition, connect a capacitor of at least  $0.47\mu F$  or more to the AC\_VRMS pin. An internal resistor is provided to generate the 65% and 45% voltages of the AC\_VRMS pin voltage, and when this external capacitance value is too small, discharge may make peak hold impossible.

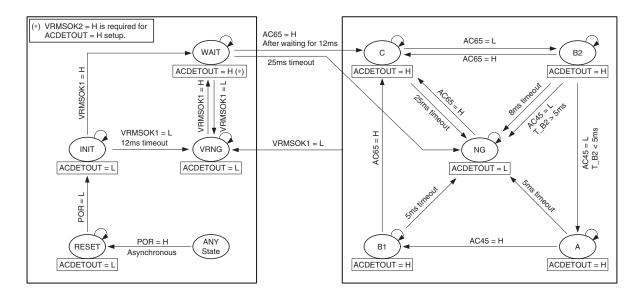

Fig. 2-2 shows the state transition diagram for the AC OFF detection circuit. The state transition conditions are related to the POR, AC65, AC45, VRMSOK1 and VRMSOK2 input signals, and the timer values in each state. POR is the IC reset signal, and AC65, AC45, VRMSOK1 and VRMSOK2 are the outputs of each comparator shown in Fig. 2-1.  $1\mu s \times 16$  times filter processing is applied to these signals. The state transition logic operating frequency is 7.8kHz.

In addition, regardless of the state transitions shown in Fig. 2-2, VRMSOK2 = High (AC\_VRMS pin voltage > 1.95V) must be set up to obtain AC\_DETOUT = High output at start-up. After VRMSOK2 = High is detected (1ms × 3 times), AC\_DETOUT goes High.

Fig. 2-2. AC Detection State Transition Diagram

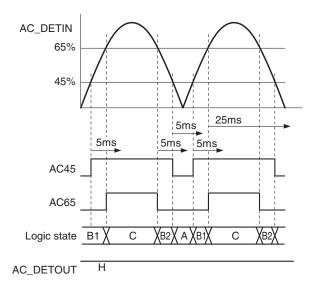

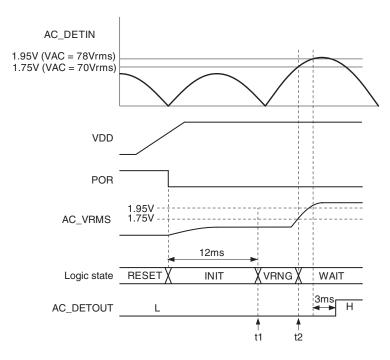

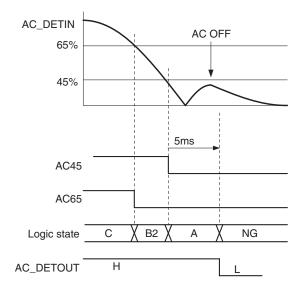

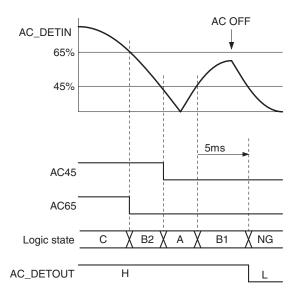

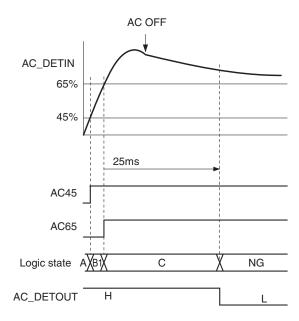

The AC\_DETOUT pin is the output signal for this function, and outputs High when the AC input state is normal, or Low when AC OFF or other abnormal state is detected. Fig. 3 shows an image of the state transitions when normal AC input continues.

Fig. 3. AC\_DETIN Input Waveform and State Transitions

In Fig. 3, the internal logic signal transitions as follows.

- When the AC input rises to 65% or more within 5ms after the state transitions to "B1", the state transitions to "C".

- When the AC input falls to 65% or less within 25ms after the state transitions to "C", the state transitions to "B2".

- When the AC input falls to 45% or less within 5ms after the state transitions to "B2", the state transitions to "A".

- When the AC input rises to 45% or more within 5ms after the state transitions to "A", the state transitions to "B1".

When the above cycle repeats, AC\_DETOUT continues to output High.

Other behaviors during start-up or AC voltage OFF are described on the following pages.

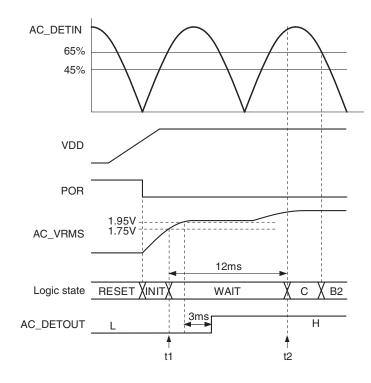

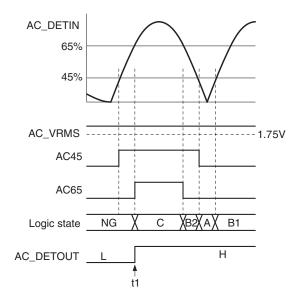

#### ♦ During normal start-up

- When POR is canceled after power-on, the state transitions to "INIT". AC\_DETOUT is Low output in the "RESET" and "INIT" states.

- When the AC\_VRMS pin voltage rises to 1.75V or more in the "INIT" state, the state transitions to "WAIT" (t1), but AC\_DETOUT continues to output Low until the AC\_VRMS pin voltage reaches 1.95V.

- When the AC\_VRMS pin voltage rises to 1.95V after the state transitions to "WAIT", VRMSOK2 goes High, and then AC\_DETOUT outputs High 3ms after that.

- When the AC\_DETIN pin voltage exceeds 65% of the AC\_VRMS pin voltage after 12ms have elapsed in the "WAIT" state, the state transitions to "C" (t2) and the normal state judgment cycle starts.

#### SONY

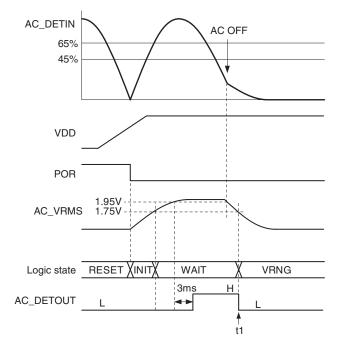

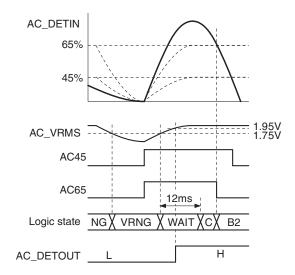

#### ♦ Start-up when the AC voltage is low

- When the AC\_VRMS pin voltage does not reach 1.75V within 12ms in the "INIT" state after POR is canceled, an AC input error is judged, the state transitions to "VRNG", and AC\_DETOUT continues to output Low (t1).

- When the IC detects that the AC\_VRMS pin voltage has risen to 1.75V or more in the "VRNG" state, the state transitions to "WAIT" (t2). Then, AC\_DETOUT outputs High 3ms after the AC\_VRMS pin voltage rises to 1.95V or more.

#### ♦ When AC OFF occurs in the "WAIT" state (1)

• When the AC\_VRMS pin voltage falls to 1.75V or less in the "WAIT" state, AC OFF is judged, the state transitions to "VRNG", and AC\_DETOUT outputs Low (t1).

#### SONY

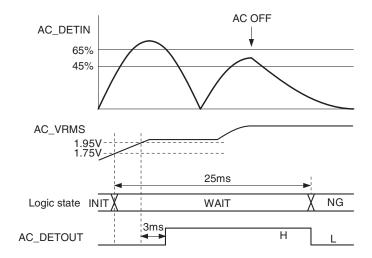

#### ♦ When AC OFF occurs in the "WAIT" state (2)

When the AC\_VRMS pin voltage is 1.95V or more but the AC\_DETIN pin voltage has not reached 65% of the AC\_VRMS pin voltage (the state has not transitioned to "C") within 25ms after the state transitions to "WAIT", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT outputs Low.

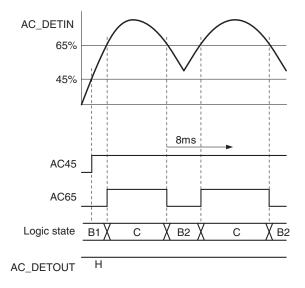

### ♦ During normal AC input

- When the AC\_DETIN pin voltage rises to 65% or more of the AC\_VRMS pin voltage within 8ms after the state transitions to "B2", the state transitions to "C".

- AC\_DETOUT continues to output High even when the "C" → "B2" → "C" cycle repeats.

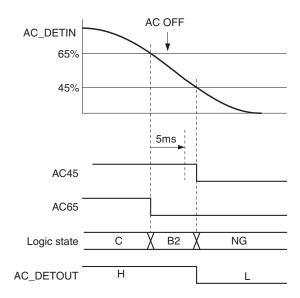

#### ♦ AC OFF in the "A" state

When the AC\_DETIN pin voltage does not rise to 45% or more of the AC\_VRMS pin voltage within 5ms after the state transitions to "A", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT outputs Low.

#### ♦ AC OFF in the "B1" state

When the AC\_DETIN pin voltage does not rise to 65% or more of the AC\_VRMS pin voltage within 5ms after the state transitions to "B1", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT outputs Low.

### ♦ AC OFF in the "B2" state (1)

• When 5ms or more have elapsed by the time the AC\_DETIN pin voltage falls to 45% or less of the AC\_VRMS pin voltage after the state transitions to "B2", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT outputs Low.

### ♦ AC OFF in the "B2" state (2)

When the AC\_DETIN pin voltage does not rise to 65% or more or fall to 45% or less of the AC\_VRMS pin voltage within 8ms after the state transitions to "B2", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT outputs Low.

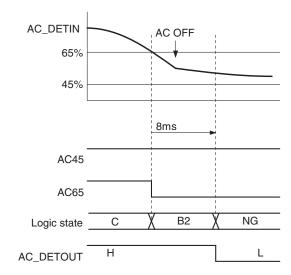

#### ♦ AC OFF in the "C" state

When the AC\_DETIN pin voltage does not fall to 65% or less of the AC\_VRMS pin voltage within 25ms

after the state transitions to "C", AC OFF is judged, the state transitions to "NG", and AC\_DETOUT

outputs Low.

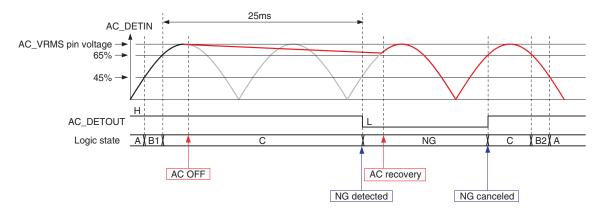

### ◆ Return to the normal cycle from the "NG" state (1)

When the AC\_DETIN pin voltage rises to 65% or more of the AC\_VRMS pin voltage while the AC\_VRMS pin voltage is 1.75V or more in the "NG" state, the state transitions to "C", AC\_DETOUT outputs High, and the normal state judgment cycle starts. (t1)

#### ◆ Return to the normal cycle from the "NG" state (2)

- When the AC\_VRMS pin voltage falls to 1.75V or less in the "NG" state, the state transitions to "VRNG".

- When AC is input again and the AC\_VRMS pin voltage rises to 1.75V or more, the state transitions to "WAIT", Then, when the AC\_VRMS pin voltage rises further to 1.95V, AC\_DETOUT outputs High. After that, when the AC input rises to 65% or more, the state transitions to "C" and the normal state judgment cycle starts.

#### ◆ Return to the normal cycle after the state transitions from "C" to "NG"

The return sequence from the "NG" state when the "C" state has continued for 25ms or more is as

follows. Operation returns to the normal cycle when the AC\_DETIN pin voltage falls below 65% of the

AC\_VRMS pin voltage, and then exceeds 65% of the AC\_VRMS pin voltage again after that.

#### 3. MODE Pin Voltage Detection Circuit Block

Normal sequence mode and standby mode can be set in accordance with the MODE pin input voltage. Normal sequence mode can be set by short-circuiting the MODE pin to GND, and standby mode can be set by short-circuiting the MODE pin to VCC or leaving the pin open.

Note that this IC has a test mode used to set the minimum resonant controller. It is possible to operate only the resonant controller by setting the MODE pin voltage to the following voltage range.

In addition, the mode transition setup times when the MODE pin voltage is switched are as follows.

• Normal sequence mode  $\Rightarrow$  Standby mode :  $128\mu s \times 2$  times • Standby mode  $\Rightarrow$  Normal sequence mode :  $128\mu s \times 2$  times

+ internal logic setup time of 320µs to 448µs

• Normal sequence mode  $\Rightarrow$  Test mode :  $128\mu s \times 3$  times • Standby mode  $\Rightarrow$  Test mode :  $128\mu s \times 3$  times • Test mode  $\Rightarrow$  Normal sequence mode :  $128\mu s \times 3$  times • Test mode  $\Rightarrow$  Standby mode :  $128\mu s \times 3$  times

#### 4. PFC\_OK Signal Output Circuit Block

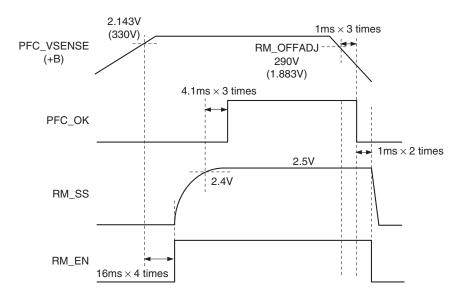

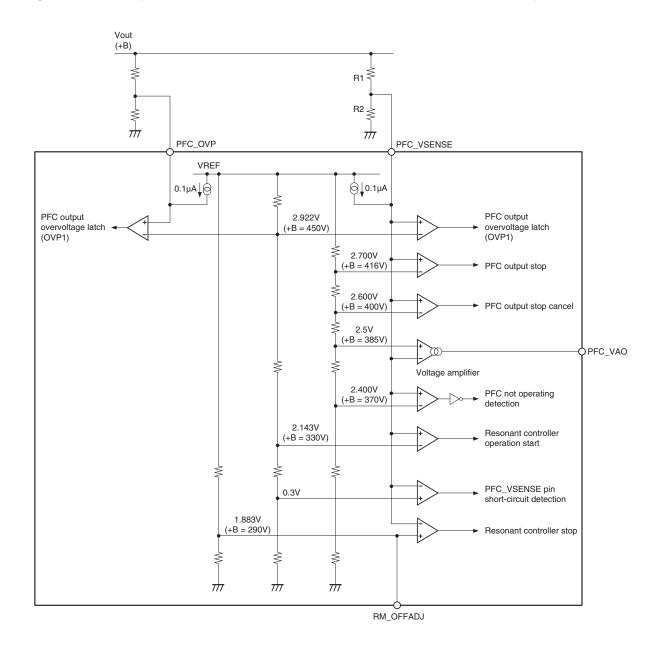

When the PFC output voltage (+B) rises to 330V or more, the resonant circuit operates, and the end of resonant soft start is detected, the PFC\_OK signal goes to High output. In this IC the PFC\_OK signal is controlled to High output by detecting that the RM\_SS pin voltage is 2.4V (typ.) or more (4.1ms  $\times$  3 times). In addition, when the IC detects that the PFC output voltage has fallen to the voltage set by the RM\_OFFADJ pin (default: 290V) or less (1ms  $\times$  3 times), the PFC\_OK signal is Low output.

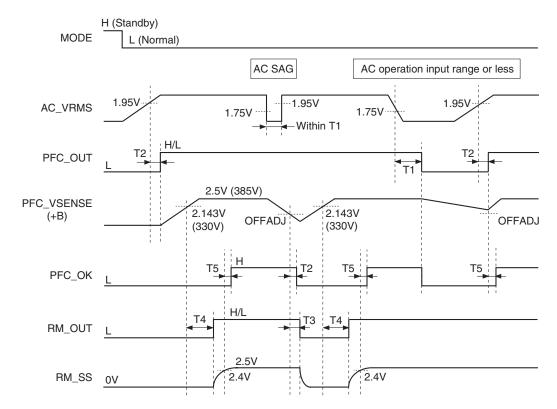

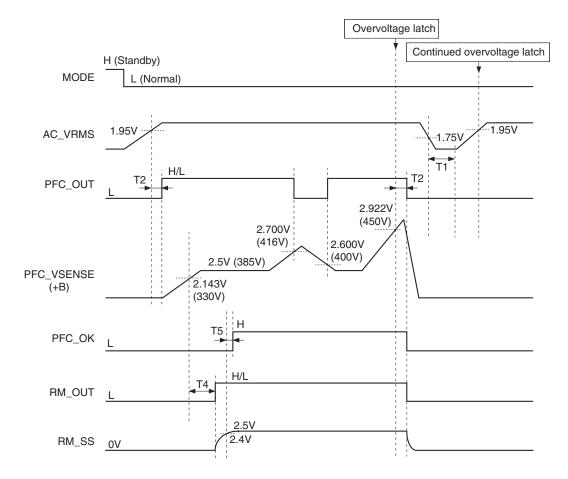

Fig. 4 shows the PFC\_OK signal output timing chart.

In addition, the PFC\_OK signal is also Low output during the following operations.

- · During NG latch

- When transition to standby mode

- ◆ When the PFC circuit is stopped (after AC\_VRMS < 1.75V, 66ms × 8 times is set up)</li>

Fig. 4. PFC\_OK Signal Output Sequence

#### ♦ PFC Block

#### 5. PFC Control Circuit Block

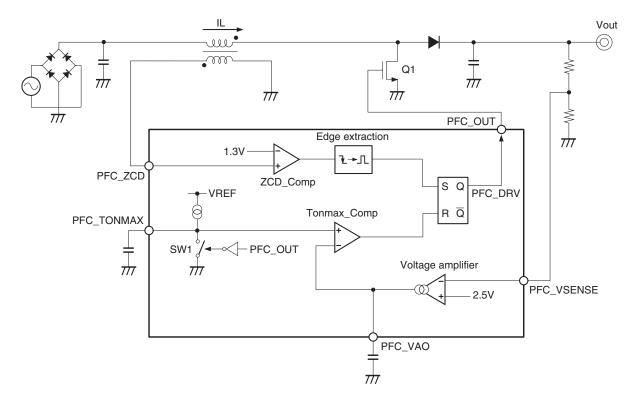

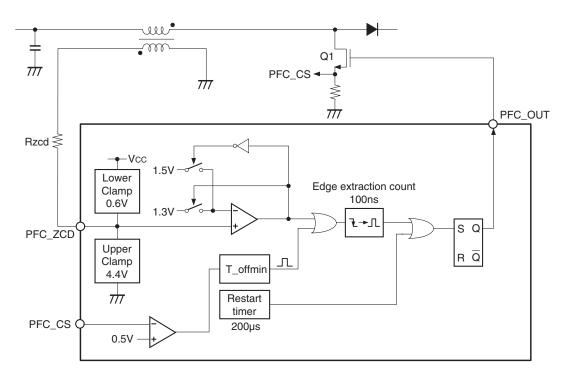

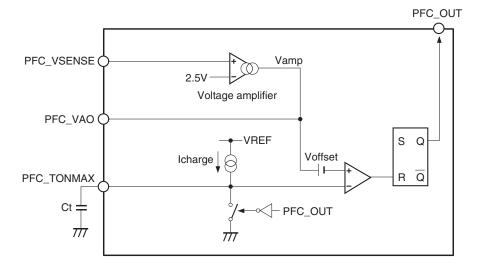

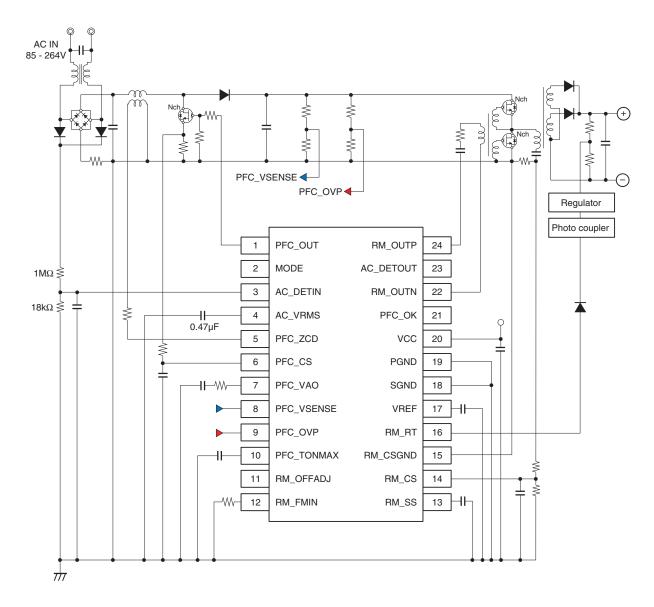

This IC has a Power-factor Correction (PFC) controller using a boost converter circuit that operates in multiplierless Critical Conduction Mode (CRM). Fig. 5 describes an overview of operation.

Fig. 5. Operation Circuit Block Diagram

This IC performs critical conduction mode switching operation that applies self-oscillation without using an oscillator. Fig. 6 shows the output waveform of each block in the steady state.

- t1: When MOSFET Q1 goes ON, SW1 goes OFF, and the inductor current (IL) rises from zero at the slope Vin/L.